Frequenz- und Puls-Kodierung

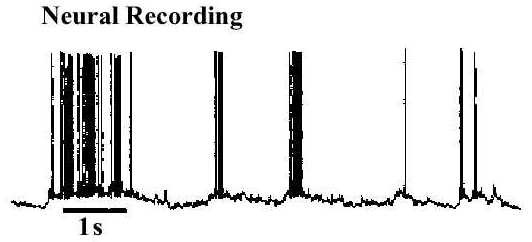

Künstliche Neuronale Netze kodieren standardmässig Input- und Outputwerte durch Amplitudenstärken, die durch natürliche oder reelle (Maschinen)-Zahlen beschrieben werden. Biologische Neuronale Netze verwenden jedoch Frequenzkodierungen in Form von Pulsen, d.h. zeitlich, binäre Kodierungen (siehe nachfolgende Abbildung). Neurone diesen Typs werden als Spiking Neurons bezeichnet, wobei auch Modellierungsansätze für diesen Typ existieren (z.B. SpikeNET).

Obwohl amplituden- als auch pulskodierte Neuronale Netze bezüglich ihrer theoretischen Computingfähigkeiten als äquivalent eingeschätzt werden, da umkehrbare, berechenbare Funktionen existieren, die Kodierungen des einen Typs in Kodierungen des anderen Typs umwandeln können, mehren sich die Hinweise, dass pulskodierte Ansätze zumindest im Signal-Processing und primären Recognition-Aufgaben, d.h. der sensornahen Verarbeitung, amplitudenkodierten Ansätzen überlegen ist, ohne dass hierfür bislang theoretische Begründungen existieren.

Berger-Liaw-NN

Binäre oder Weightless NN

Effiziente Nutzung digitaler HW

Der Grund, warum Spiking-NN und Binäre NN besonders betrachtet werden sollten, liegt neben den oben dargestellten Vorteilen der Repräsentation in der effizienten Umsetzung von Netzwerkmodellen im Rahmen gegebener digitaler Hardware. Pulskodierte Netze, die mit dem Softwaresystem SpikeNET erstellt werden, können Millionen Neurone und Milliarden von Verbindungen enthalten. Kleinere pulskodierte Netze können die Taktfrequenz der digitalen Hardware effizient nutzen, d.h. Spike-Intervalle, die bei grossen NN auf einen ms-Bereich eingestellt werden, können dann im GHz-Bereich operieren.

Binäre NN zeichnen sich vor allem dadurch aus, dass sie den vorhandenen Speicher wesentlich effizienter nutzen können als Netzmodelle, die reelle Gewichte verwenden.

Designräume der Spiking-NN und der Binären NN

Der allgemeine Ansatz dieses Software-Projektes besteht in dem Aufbau von Designräumen für Spiking-NN sowie für Binäre NN und der aktiv-evolutionären Suche nach NN-Architekturen als Punkte in einem solchen Designraum, die bestimmte Anforderungen, kodiert in einer Evaluationsfunktion, optimal erfüllen. Schwerpunkt sollen dabei die Spiking-NN bilden, da sie aus der momentanen Sicht den leistungsfähigeren Ansatz darstellen.

Segundo et al. (1995:955) definieren ein "Synaptic Coding" als eine Relation zwischen Prä- und Postsynaptischen Aktivitäten, wobei individuelle Synapsen individuelle Kodierungen besitzen. Synaptische Kodierungen lassen sich als puls-kodierte Transferfunktion interpretieren, die einen präsynaptischen, pulskodierten Input in einen postsynaptischen, pulskodierten Output transformieren, wobei die Transferfunktion durch einen Lernprozess erworben wird, der die bislang existierende Aktivitäten an der betrachteten Synapse und an verbundenen Synapsen berücksichtigt. D.h. eine synapsenindividuelle, puls-kodierte Transferfunktion ist eine zeitlich nicht-stationäre Funktion, da alle Aktivitäten an und um die Synapse die Transferfunktion beeinflussen, die sich somit in einem permanenten Adaptionsprozess befindet.

Wird die puls-kodierte Transferfunktion durch eine parametrisierte Funktion beschrieben, so ist ein EA wie die Evolutionsstrategie in der Lage, individuelle Transferfunktionen parallel zu einer individuellen Netzarchitektur zu finden. Als Augangspunkt kann hierfür beispielsweise die EVASION-Methode zur Strukturierung von NN durch ES dienen (Rechenberg (1994:182ff).

Wird anstatt einer parametrisierten Funktion ein Transferprogramm verwendet, so kann durch diese Verallgemeinerung eine GP/HP-Suche durchgeführt werden, wobei eine Multi-Populationenstrategie sinnvoll ist, wenn die Synapsenprogramme eines Netzes als Population betrachtet wird.

Das Softwaresystem SpikeNET, das in C++ implementiert ist, könnte in diesem Zusammenhang auf seine Eignung als Simulations- und Evaluationssystem im Rahmen eines EA untersucht werden, wobei beachtet werden muss, dass es sich nach dem momentanen Kenntnisstand nicht um eine Open-Source handelt. Demgegenüber könnten andere Softwaresysteme (siehe NN-FAQ5) auf ihre Eignung geprüft werden, wobei die dort beschriebenen Systeme nahezu alle auf amplitudenkodierten Modellen basieren. Eine Spiking-NN-Description-Language, mit dem ein GP/HP-System Modelle formulieren könnte, die danach evaluiert werden, existiert demgegenüber zum jetzigen Zeitpunkt nicht. Es könnte geprüft werden, ob sprachliche Konstrukte einer High-Level NN-Beschreibungssprache wie z.B. nn/xnn benutzt werden könnten, um eine Spiking-NN-Description-Language zu erzeugen, die durch einen EA manipuliert werden kann.

Berger-Liaw-NN-Software-Clon

Allgemeine Signalverarbeitung mit Berger-Liaw-NN

Der Ansatz des Berger-Liaw-NN ist nicht auf eine Sprachverarbeitung beschränkt, sondern kann für jede Form von Zeitreihen verwendet werden. Es besteht hierbei ein direkter Zusammenhang zu der Aufgabenstellung einer nicht-linearen Zeitreihenanalyse im Rahmen des Software-Projekt SW09 "EA und Chaos-Theorie". Bei diesem Teilprojekt soll geprüft werden, ob durch GP/HP Analyse-Algorithmen erzeugt werden können, die denen gleichwertig oder überlegen sind, die im Rahmen der Chaos-Theorie erstellt wurden. Die Verwendung von Spiking-NN ist demgegenüber eine Einschränkung gegenüber der freien Algorithmenerzeugung durch symbolische GP bzw. CPG oder allgemeiner HIMC (siehe Software-Projekt SW02).

Pulskodierte GP-Programme und GP-Kodierungsprogramme

Als Alternative zu dem Aufbau von NN-Designräumen könnte ein vollständig GP-orientierter Ansatz erwogen werden. Es soll zwischen den folgenden Strategien unterschieden werden, wobei ein HIMC-System (siehe Software-Projekt SW02) unterstellt wird:

- Erzeugung von HIMC-Programmen, die pulskodierten Input verarbeiten können.

- Erzeugung von Kodierungsprogrammen durch ein HIMC-System, das zunächst eine Pulskodierung erzeugt, die von einem nachgeschalteten Spike-NN verarbeitet werden.

- Erzeugung von Kodierungsprogrammen durch ein HIMC-System, das zunächst eine Pulskodierung erzeugt, die von einem nachgeschalteten HIMC-Signalverarbeitungsprogramm verarbeitet wird.

Der erste Ansatz erfordert, dass pulskodierte Inputdaten vorliegen, d.h. es muss extern eine Kodierungsmethode vorgegeben und angewendet werden. Im Rahmen des zweiten Ansatzes kann zusätzlich ein evolutionäres Konfigurationssystem auf der Ebene der Spike-NN eingeführt werden, das in einem oben beschriebenen Designraum arbeitet. Die Kombinationsmöglichkeiten eines solchen zwei-gliedrigen Verfahrens beinhaltet auch die Verwendung koevolutionärer Verfahren, indem HIMC-Kodierungsprogramme und ein Spike-NN je als Mitglieder einer eigenen Spezies betrachtet werden, die sich symbiotisch zu einem Organismus zusammenschliessen, in dem sequentiell ein Kodierungs- und ein Spike-NN integriert sind. Diese Möglichkeit besteht auch für den dritten Ansatz, der grössere Designfreiheit besitzt als der zweite Ansatz, da die Signalverarbeitungsprogramme nicht die Struktur eines Spike-NN besitzen müssen.

Beziehung zur Hardware

Spiking-1-Synapsen-Transistor

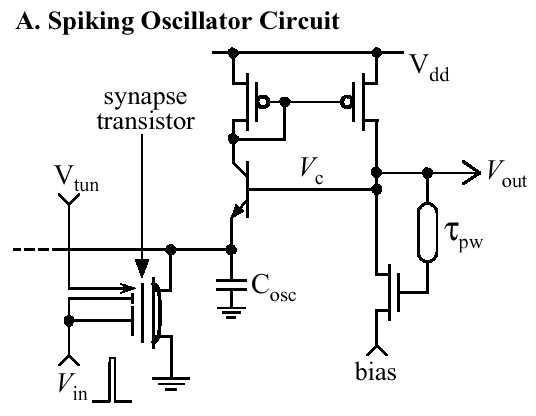

In Diorio (1997: 106ff) wird ein analoger Schaltkreis formuliert, der einen 1-Synapsen-Transistor (1SyT, siehe Hardware-Projekt HW04) als Element beinhaltet, und der als Spiking-Oscillator arbeitet (siehe nachfolgende Abbildung). Dies bedeutet, dass ein 1SyT im Prinzip auch als Spiking-Synapse eingesetzt werden kann, wodurch ein Spiking-1SyT entsteht.

In diesem Zusammenhang können aktiv-evolutionäre Verfahren eingesetzt werden, um Spiking-1SyT-Architekturen und Architekturen aus Spiking-1SyT zu erzeugen, genauso wie durch aktiv-evolutionäre Verfahren 1SyT-Architekturen mit bestimmten Eigenschaften gesucht werden, wie grösserer Auflösung der analogen Gewichte, oder Implementierbarkeit in einer Vertikal-Transistor-Technologie (für Details siehe Hardware-Projekt HW04).

EHW-Clon von Hippocampusmodell

Ein besonderer Ansatz würde sich ergeben, wenn die Neuron-Chips des Berger-Liaw-NN verfügbar und kostengünstig wären. In einem solchen Szenario könnten diese Chips auf Tochterkarten auf das Free Evolvable Motherboard gesetzt werden. Ein EA könnte dann die Verbindung der Chips und die individuelle Ausprägung der einzelnen Chips ermitteln, um bestimmte Aufgaben zu lösen.

Dieses Szenario ergibt sich in analoger Form auch im Fall des Clonens durch EHW, wobei dies den Vorteil hätte, dass das Gesamtsystem direkt in einer rekonfigurierbaren HW implementierbar ist.

Referenzen

Diorio, Chris: Neurally Inspired Silicon Learning: From Synapse Transistors to Learning Arrays, . 1997.

Rechenberg, Ingo: Evolutionsstrategie '94, Stuttgart, 1994.

Ludermir, T. B. ; de Carvalho, A. ; Braga, A. P. ; de Souto, M. C. P. : Weightless Neural Models: A Review of Current and Past Works. NEURAL COMPUTING SURVEYS Vol. 2, 1999, S. 41 - 61.

Segundo, J.P.; Stiber, M.; Vibert, J.-F.: Synaptic Coding of Spike Trains. In: Arbib, Michael A.: The Handbook of Brain Theory and Neural Networks. MIT-Press, 1995, S. 953 - 956.