Analoger 1-Synapsen-Transistor (1SyT)

Die Hauptfrage, die im Rahmen der momentanen Entwicklung evolutionärer Hardware (EHW) steht, betrifft die Ebene, auf der die Evolutionsprozesse aktiv eingreifen. Paul Layzell ist der Ansicht, dass der Transistorlevel die geeignete Ebene ist, um eine intrinsische EHW mit einer maximalen Flexibilität zu erhalten.

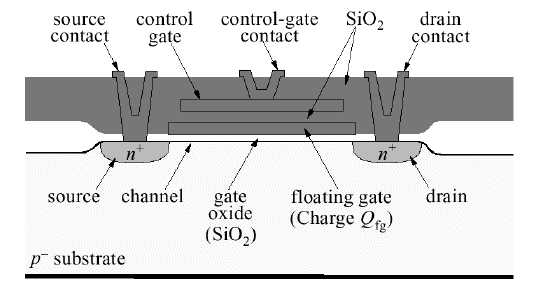

Im Rahmen dieses Projektes soll der Frage nachgegangen werden, ob EHW-Systeme auf der Basis von analogen 1-Synapse-Transistoren (1SyT), die von Chris Diorio entwickelt wurden, die Anforderungen an eine intrinsische Evolution erfüllen können. Bei den 1SyT handelt es sich um eine Klasse von analogen Transistoren, die durch Standard-MOS-Technologien in Silizium erzeugt werden können, und die ein Gewicht speichern können, das 16 bis 18 bit entspricht. Aus Systemen dieser Synapsen lassen sich Neuronale Netze bzw. deren Gewichtsmatrix bilden, die durch verschiedene Lernverfahren adaptiert werden können.

Es sollte die Hypothese geprüft werden, dass EA als Lernverfahren eines adaptiven Systems aus 1SyT den Systemaufbau vereinfacht, da überwachtes Lernen mit EA durch die Rekombinations- und Mutations-Operationen einfacher ist, als die von Diorio entwickelten Lernverfahren.

Im Rahmen des Hardware-Projektes sollen zum einen alternative 1SyT-Architekturen untersucht werden, die bestimmte Eigenschaften besitzen, und zum anderen sollen Architekturen aus 1SyT erzeugt und untersucht werden, die 1SyT als funktionelle Building-Blocks besitzen, und zusätzliche globale Eigenschaften wie Modularisierbarkeit, EA-Konfigurierbarkeit und Skalierbarkeit besitzen.

1SyT-Architekturen

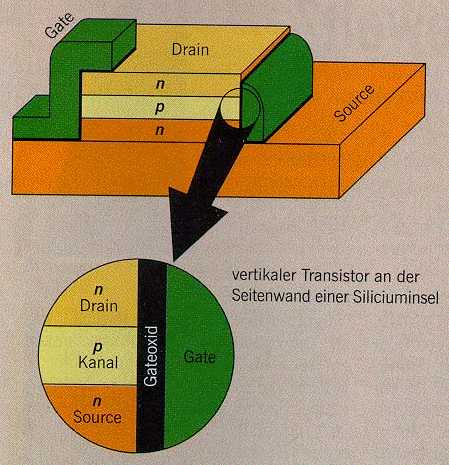

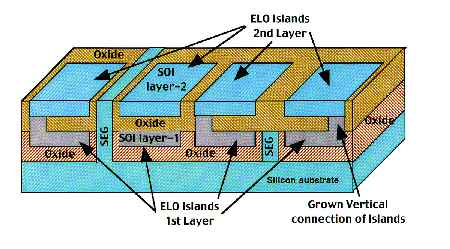

Diorio hat in seiner Dissertation Neurally Inspired Silicon Learning vier Arten von 1SyT entworfen, und verschiedene Verbesserungen vorgeschlagen. Dies deutet an, dass ein 1SyT-Designraum existiert, der mit Hilfe von EA durchsucht werden kann, um 1SyT mit bestimmten Eigenschaften zu finden. Relevante Ziele sind hierbei 1SyT, die eine grössere Auflösung ihrer Gewichte besitzen, und 1SyT, die besonders energiesparend arbeiten, was im Rahmen sehr grosser Skalierungen wichtig wird, bis hin zu Single-Wafer-Integration. Ein weiteres Kriterium ist der Platzverbrauch, d.h. es soll nach 1SyT-Designs gesucht werden, die wenig Die-Platz verbrauchen, wobei neue Verfahrensansätze wie die Vertikal-Transistor-Technologien, beachtet werden sollen (Risch et al. (1999), siehe nachfolgende Abbildung).

Diese Verfahrensansätze nutzen konventionelle Lithographieverfahren, die kompatibel zu den MOS-FET-1SyT-Designs von Diorio sind, und mit denen 50 bis 100 mal mehr Transistoren auf der gleichen Die-Fläche untergebracht werden können im Vergleich zu den gegenwärtigen Horizontal-Transistor-Technologien.

Von besonderem Interesse ist dabei, dass durch die Epitaxieverfahren Schichten von weniger als 40 A Dicke erzeugt werden, mit der Folge, dass die 1SyT-Designs richtige Tunnelprozesse nutzen können anstatt FN-Tunneln (s.a. Diorio (1997: 105)), was u.a. zu einer wesentlichen Beschleunigung der 1SyT führen würde.

Ein solcher Designraum kann durch die folgenden prinzipiellen Methoden durchsucht werden:

1) Soft-EA: Hierbei wird ein analoges Simulationssystem wie eine SPICE-Variante verwendet, um Eigenschaften eines Designs zu berechnen, das durch einen Soft-EA erzeugt wurde, ähnlich der Vorgehensweise des Designs von analogen Schaltkreisen durch ein GP-System nach John Koza.

2) Hard-EA: Ein EA erzeugt eine Population von 1SyT-Designs, die in einem Hardware-Prozess implementiert werden. Die Eigenschaften dieser physikalischen Systeme werden gemessen, anstatt berechnet zu werden. Diese Vorgehensweise hat den Vorteil, dass potentiell fehlerhafte Algorithmen und Parameter in der Simulationssoftware vermieden werden. Andererseits ist diese Vorgehensweise wesentlich teuerer und langwieriger als Simulationen. Eine solche Hard-EA könnte mit Hilfe eines Fabrikationsservice wie z.B. MOSIS (Metal Oxide Semiconductor Implementation Service) durchgeführt werden. Auf den kleinsten Chips (2 mm x 2 mm) lassen sich viele alternative 1SyT-Designs erzeugen und testen, sodass die Kosten pro Einzeldesign bei solchen Prototypimplementierungen klein gehalten werden können. Durch neuere Entwicklungen wie die Wafer-Direktbelichtung, die von Heinz Kück, Wolfgang Doleschal und Wolfram Kluge am Fraunhofer Institut für Mikroelektronische Schaltungen und Systeme (IMS) entwickelt wurde, können Prototypen noch wesentlich kostengünstiger hergestellt werden (siehe Linsmeier (1999)), wobei immer noch das Zeitproblem existiert.

3) Kombination aus Soft- und Hard-EA, eventuell unter Verwendung weiterer Strategien wie dem Aktiven Lernen und dem Optimal Experiment Design. Eine Strategie der Kombination besteht darin, den Designraum durch Software-Simulation einzugrenzen, und sehr spezielle 1SyT-Designs hardwaremässig zu implementieren, sodass sehr wenige Iterationen (Generationen) notwenig werden, um optimale Ergebnisse zu erhalten. Eine alternative Strategie ist die Modelloptimierung durch Messungen an implementierten 1SyT-Designs, d.h. ausgehend von einem Standard-Simmulationsmodell werden 1SyT-Designs entwickelt, denen grosse Unsicherheitswerte zugeordnet werden können, was einem Query-by-Varianz-Maximum entspricht. Diese Designs werden implementiert, und Messungen deren Eigenschaften werden verwendet, um das Standardmodell auf den 1SyT-Designraum zu optimieren. Mit dem optimierten Modell werden im weiteren Suchprozesse durchgeführt, um 1SyT-Designs mit den gesuchten Eigenschaften zu finden.

Das Design von speziellen 1SyT unterliegt mehreren Zielanforderungen, wie z.B. grössere Gewichte, kleinere Abmessungen, geringerer Energieverbrauch, sodass es sich faktisch um eine Mehr-Ziel-Optimierungsaufgabe handelt, die durch EA in Form von MZ-EA robust gelöst werden können (siehe Bachelier (1998b), Veldhuizen (1999)). Grundlegend ist auch bei den MZ-EA das Konzept der Pareto-Optimalität, sodass in jeder Generation eine Menge von nicht-dominierenden 1SyT-Designs als Paretomenge vorliegt. Nach Abbruch des Mehr-Ziel-Optimierungsprozesses können die Designs in der dann vorliegenden Paretomenge implementiert werden, gefolgt von Messungen, bei denen physikalische Eigenschaften unter verschiedenen physikalischen Bedingungen wie z.B. Temperatur bestimmt wird. Mit Hilfe dieser Messungen muss letztendlich entschieden werden, welches Design für eine entsprechende Architektur aus 1SyT ausgewählt wird, z.B. durch ein weiteres Kriterium wie die Temperatur-Robustheit des physikalischen Systems.

Architekturen aus 1SyT

Der zweite Teilbereich des Projektes besteht in der Erforschung von Architekturen aus 1SyT, d.h. es wird untersucht, wie die 1SyT als Building-Blocks zu modularen, hierarchisierbaren und beliebig skalierbaren Architekturen zusammengesetzt werden können, die durch EA konfigurierbar sind, wodurch 1SyT-EHW entsteht. Grundsätzlich ergibt sich die Frage, ob und welche anderen Building-Blocks neben 1SyT und Verbindungsdrähte vorliegen müssen, um eine konfigurierbare Architektur zu erhalten. Ansätze hierzu sollten in der Vielzahl von bereits durchgeführten anderen EHW zu finden sein. Insbesondere das Hardware-Projekt HW03, das sich mit der analogen EHW "Evolvable Motherboard" von Paul Layzell und deren Erweiterung zu einer Free Evolvable Motherboard- Plattform beschäftigt, soll berücksichtigt werden.

Ein analoges Simulationssystem kann auf die Simulation von ausgewählten 1SyT-Architekturen spezialisiert werden, sodass Architekturen von 1SyT in Verbindung mit anderen analogen Funktionselementen simuliert werden können.

Andere Erfahrungen könnten beispielsweise aus dem Bereich der Zellulären Automaten (CA) genutzt werden, wie z.B. CAM8 , da dort die Implementierung einer beliebig skalierbaren Architektur aus einfachen Building-Blocks als Grundproblem existiert (siehe auch Software-Projekt SW08). Wird eine CA-ähnliche Struktur verwendet, so bedeutet dies, dass 1SyT lokal verknüpft werden. Weiterhin könnte das CAM-Brain-Projekt von de Garis als Vorbild verwendet werden, da dort aus CA Neurone und Neuronen-Module durch einen evolutionären Wachstumsprozess erzeugt werden, wobei die Module zu beliebig komplexen Hierarchien verknüpft werden können.

Teilprojekt: 1SyT durch Epitaxial Lateral Overgrowth

Eine Sonderaufgabe im Zusammenhang mit 1SyT-Architekturen in Silicium-Technologie ist die Prüfung, ob durch eine Verfahrenweise wie dem Epitaxial Lateral Overgrowth (ELO) von Dr. Gerold W. Neudeck, eine Architektur erzeugbar ist, die eine funktionale Äquivalenz mit einem 1SyT besitzen. Bei der ELO-Technologie handelt es sich um eine Form der Vertikal-Transistor-Technologie, die jedoch im Gegensatz zu dem Ansatz von Risch et al. (1999) massiv auf Selbstorganisationsprozesse bei dem epitaxialen Wachstum setzt. Funktionale Strukturen wachsen auf diese Weise, anstatt durch eine Sequenz aus lithographischen Belichtungen, Äzungen und Materialabscheidungen gebildet zu werden. Dies hat den Vorteil, dass bis zu 30 Einzelschritte gespart werden, was ein solches Verfahren extrem kostengünstig machen würde.

Durch die Verwendung epitaxialen Wachstums, bei dem einzelne Atomschichten abgeschieden werden können, wären 1SyT-Architekturen anwendbar, bei denen richtige Tunnelprozesse nutzbar werden (s.a. Diorio (1997: 105)).

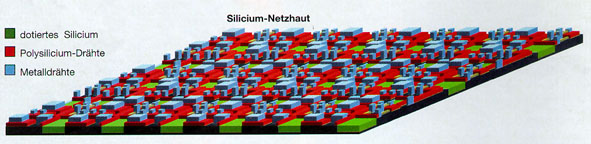

Das epitaxiale Wachstum arbeitet gleichzeitig auf der gesamten Waferfläche, sodass 1SyT-Architekturen erzeugbar wären, die bis zur Wafer-Scale-Integration skalierbar sind.

Epitaxiales Wachstum könnte unter Temperatur-Bedingungen stattfinden, die darunter liegende Strukturen unversehrt lassen. Damit wären zum ersten Mal drei-dimensionale Transistor-Strukturen auf der Basis von Silicium denkbar, während bei den herkömmlichen lithographischen Techniken Zwischenschritte existieren, die durch ihre thermischen Bedingungen weiter unten liegende Strukturen beschädigen würden. Im Zusammenhang mit den 1SyT würden drei-dimensionale 1SyT-Architekturen bedeuten, dass Synapsendichten erreichbar sind, die denen in biologischen Systemen mit 3 x 10^8 Synapsen pro Kubikmillimeter überlegen sind (siehe Diorio (1997: xv)). Erst das Zusammenwirken drei-dimensionaler Si-Strukturen, Wafer-Scale-Integration und die wesentlich höhere Schaltgeschwindigkeit, können Ziele wie das Brain-Building, das dem CAM-Brain-Projekt von de Garis zugrunde liegt, realisierbar machen.

Diese Frage nach einer solchen 1SyT-Architektur ist nicht isoliert von der Frage nach einer Architektur aus 1SyT, da bei dem ELO alle Building-Blocks gleichzeitig und parallel wachsen.

Teilprojekt: Magnetoelektronische 1SyT-Architekturen

Im Hardware-Projekt HW06 wird evolutionäre Hardware auf der Basis von magnetoelektronischen Elementen untersucht. In diesem Zusammenhang sollte auch geprüft werden, ob ein 1SyT auf der Basis von Konfigurationen von Schichten unterschiedlicher magnetischer Eigenschaften möglich ist (1-Synapsen-Spin-Transistor, 1SySpT).

Der Vorteil einer solchen Architektur besteht insbesondere darin, dass Speicherzustände unabhängig von einer externen Stromquelle sehr lange erhalten bleiben. 1SyT auf der Basis von MOS-FETs, wie sie von Chris Diorio entwickelt wurden, sind zwar auch nicht-flüchtig, doch die Stabilität und Robustheit wäre bei einer magnetoelektronischen Implementierung einer 1SyT wesentlich grösser.

Ein potentieller Vorteil einer 1SySpT-Implementierung ist, dass die funktionalen Einheiten kleiner sind als bei einer MOS-FET-Implementierung, da zumindest eine magnetoelektronische 1Bit-Speicherzelle quasi eine horizontale Implementierung ist, ähnlich der Vertikal-Transistor-Technologie von Risch et al. (1999) oder den Architekturen, die durch Epitaxial Lateral Overgrowth (siehe Dr. Gerold W. Neudeck) entstehen.

Spin-Transistoren besitzen Schalt- und Rekonfigurierungzeiten, die im ns-Bereich liegen. Ob diese Eigenschaft bei analogen 1SySpT zu einer Performanceverbesserung führt, muss im Rahmen der Kooperation beider Hardware-Projekte überprüft werden, da eine proportionale Performanceverbesserung mit Steigerung der Systemfrequenz bei analogen Systemen nicht notwendig eintritt.

Teilprojekt: Nicht-Standard-Materialien für 1SyT

Im Hardware-Projekt HW07 werden Nicht-Standard-Materialien auf ihre Eignung getestet, Systeme mit analogen Computing-Fähigkeiten zu bilden, wie dotierte Polymere, Kohlenstoff-Nanoröhren und modifizierte DNA-Materialien. Diese Matierialien, die in organischen Lösungen vorliegen, werden durch unterschiedliche Verarbeitungstechniken strukturiert, wie Tintenstrahl- oder Offset-Druck oder durch Schreiben mit Nanfedern.

Gelingt es funktionale Einheiten wie Transistoren, mit diesen Materialien und angepassten Verarbeitungstechniken zu erzeugen, so könnte versucht werden, Grundeinheiten zu erzeugen, die funktional äquivalent zu einem 1SyT oder 1SyT-Varianten mit bestimmten Eigenschaften wie grösserer Gewichtsauflösung sind.

1SyT-Varianten, die durch ein aktiv-evolutionäres Suchverfahren und ein Simulationssystem gesucht werden sollen, beziehen sich auf eine grössere Gewichtsauflösung der Einzel-Synapse. Im Rahmen des Entwicklungssystems für EA (Software-Projekt SW01) und für SOMs (Software-Projekt SW03) wurde bereits auf die Bedeutung von Intervallen als Alternative zu den reellen Maschinenzahlen eingegangen, mit denen Input- und Outputvariablen belegt werden sollten, wenn durch Messung ermittelte, reale Evaluierungsbeispiele (Fitnescases) bzw. Trainingsbeispielse vorliegen. In Verbindung mit den Intervallen werden Intervall-Arithmetiken verwendet, um numerische Instabilitäten, die durch Rundungsoperationen auf Maschienenzahlen entstehen, zu vermeiden.

Im Rahmen eines Teilprojektes soll untersucht werden, ob die Hardware-Technologie der analogen 1SyT in der Lage ist, Intervalle zu verwenden, und Intervall-Arithmetiken zu implementieren. Für die 1SyT bedeutet dies zum einen, ob die Gewichtsauflösung so weit gesteigert werden kann, dass damit Intervalle repräsentiert werden können, womit jedoch kaum gerechnet werden kann. Realistischer sind 1SyT-Systeme, d.h. Verknüpfungen von 1SyT und eventuell weiteren analogen Schaltungen, die zusammen ein Intervall repräsentieren können, und mit denen als Basiselement Intervall-Arithmetiken möglich werden.

Denkbar wäre als erster Schritt die Verwendung eines analogen Simulationssystems wie SPICE und ein spezialisiertes GP-System von John Koza, um zu erkunden, ob konventionelle, analoge Systeme zur Intervall-Repräsentation und zu Intervall-Arithmetiken verwendbar sind. In Koza et al. (1999: 815ff) werden verschiedene analoge Computational Circuits wie Wurzelbildung, Logarithmus oder Gauss-Funktion vorgestellt, die mit diesem System erzeugt wurden.

Gelingt der Nachweis, dass Intervall-Repräsentation und Intervall-Arithmetiken analog implementierbar sind, so kann ein modifiziertes, analoges Simulationssystem, das 1SyT-Varianten als Basiselemente verwendet, in Verbindung mit einem evolutionären System benutzt werden, um 1SyT-Architekturen zu suchen, die diese Anforderungen erfüllen.

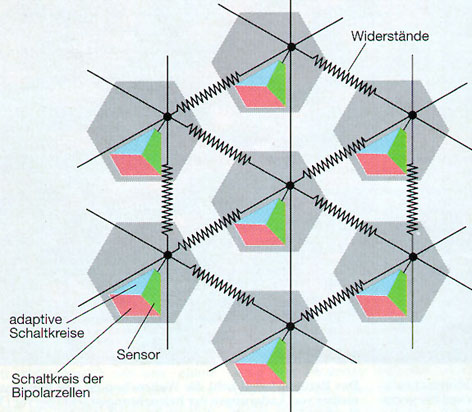

Chris Diorio ist Teil der Gruppe "Physics of Computation" von Carver Mead, der an der Umsetzung von biologischen Informationsverarbeitungssystemen durch analoge VLSI-Technologien arbeitet. In diesem Zusammenhang sind z.B. Modelle der Retina (siehe nachfolgende Abbildung) und der Cochlea entstanden.

Im Gegensatz zu den Synapsen-Transistoren handelt es sich dabei um integrierte Systeme aus Sensoren und Processing-Elementen, d.h. ein Einzelelement (Sensor-Processor-Zelle) dieser Modelle besteht aus einem Sensorelement und einer Architektur aus 1SyT, die eine direkte und lokale Verarbeitung der lokalen Sensordaten durchführen (siehe nachfolgende Abbildung). Die Ergebnisse der lokalen Verarbeitung werden an externe Verarbeitungseinheiten ausgelesen. Es besteht auch die Möglichkeit, dass lokale Verarbeitungen in Abhängigkeit von den Zuständen benachbarter Zellen durchgeführt werden, ähnlich wie bei Zellulären Automaten (siehe auch Software-Projekt SW08).

Ein Teilprojekt könnte analoge Simulationssysteme wie 1SyT-SPICE um Sensor-Elemente erweitern, in Verbindung mit einem GP-System (siehe John Koza), das Verarbeitungselemente und Sensorelemente konfiguriert, wobei die Evaluation durch das Simulationsystem durchgeführt wird.

Als Sensoren könnten beispielsweise Photodioden oder spezielle Single-Electron-Transistor(SET)-Varianten wie ein Radio-Frequency-(RF)-SET nach Daniel E. Prober (Yale University; siehe auch Science 22.Mai 1998) eingesetzt werden, wobei Letzteres sich durch eine extreme Empfindlichkeit der Detektion von Photonen auszeichnet, bei einer enormen Frequenz-Bandbreite (von Röntgenstrahlung bis zu Mikrowellen). Ausserdem sind Messraten von bis zu 100 Megahertz möglich, und ein RF-SET könnte zudem als Spektrometer eingesetzt werden. Im Rahmen der Nutzung von RF-SETs könnte zudem geprüft werden, ob Design-Varianten oder Designprinzipien genutzt werden könnten, um damit 1SyT-Varianten zu erzeugen, wobei in beiden Architekturen ein Tunnelprozess genutzt wird. Auf diese Weise könnte das Sensor-Subsystem und das Processing-Subsystem durch ähnliche Verfahrensschritte erzeugt werden.

Denkbar wäre beispielsweise die Möglichkeit, neben Sensor- und Processing-Elementen auch Aktor-Elemente in eine Zelle zu integrieren. Wird dieser Aufbau eines optischen Systems betrachtet, so würde dies beispielsweise die Integration einer Photodiode oder eines Mikro-Lasers bedeuten. Mikro-Laser können beispielsweise durch Lithographie-Techniken als Quanten-Chaos-Laser erzeugt werden (siehe Jens Nöckel, siehe nachfolgende Abbildung) oder es sind Mikro-Laser auf Polymerbasis möglich, die durch Verarbeitungstechniken wie dem Mikro- und Nano-Stempeln, erzeugt werden können (siehe auch Hardware-Projekt HW07).

Mit einer solchen optoelektronischen Sensor-Prozessor-Aktor-Architektur könnten extrem leistungsfähige Verarbeitungsarchitekturen erzeugt werden, indem die Sensor-Aktor-Elemente für die nicht-lokale Kommunikation zwischen einzelnen Chips verwendet wird. Die emitierten, optischen Signale eines Chips können durch Hologramme an mehrere andere Chips verteilt werden, welche die Signale verarbeiten, und durch ihre optischen Aktoren die Ergebnisse wieder an andere Chips versenden. Die optische Verknüpfung ermöglichst eine vollständige Parallelisierung, ohne dass eine Chipfläche hierfür aufgewendet werden muss. Würde dies auf den Chips integriert, so würde dies die Fläche dominieren, d.h. es wären wesentlich mehr Flächeneinheiten für Verbindungen als für Sensor-Prozessor-Aktor-Zellen notwendig. Durch den Austausch bzw. Rekonfiguration der Hologramme sind zudem flexible, direkte Verbindungsarchitekturen möglich.

Sollten photonische Prozessorelemente verwendet werden (siehe Hardware-Projekt HW08), so könnten alle drei Subsysteme auf optischer Basis arbeiten, ohne dass eine Umwandlung von optischen zu elektrischen Signalen notwendig wäre.

Referenzen

Layzell, Paul : A New Research Tool for Intrinsic Hardware Evolution. In: Proceedings of Second Int. Conf. on Evolvable Systems: From Biology to Hardware (ICES98) September, 1998.

Koza, J.R; Bennett, F.H.; Andre, D.; Keane, M.A.: Genetic Programming III. Morgan Kaufmann, 1999.

Risch, L.; Rösner,W.; Schulz, T.: Transistor verkehrt. In: Spektrum der Wissenschaft, 6/1999, S. 94f.